# 4K Memory for Mark-8 Minicomputer

By Bryan Blackburn Copyright © 2003, http://members.cox.net/oldcomp/

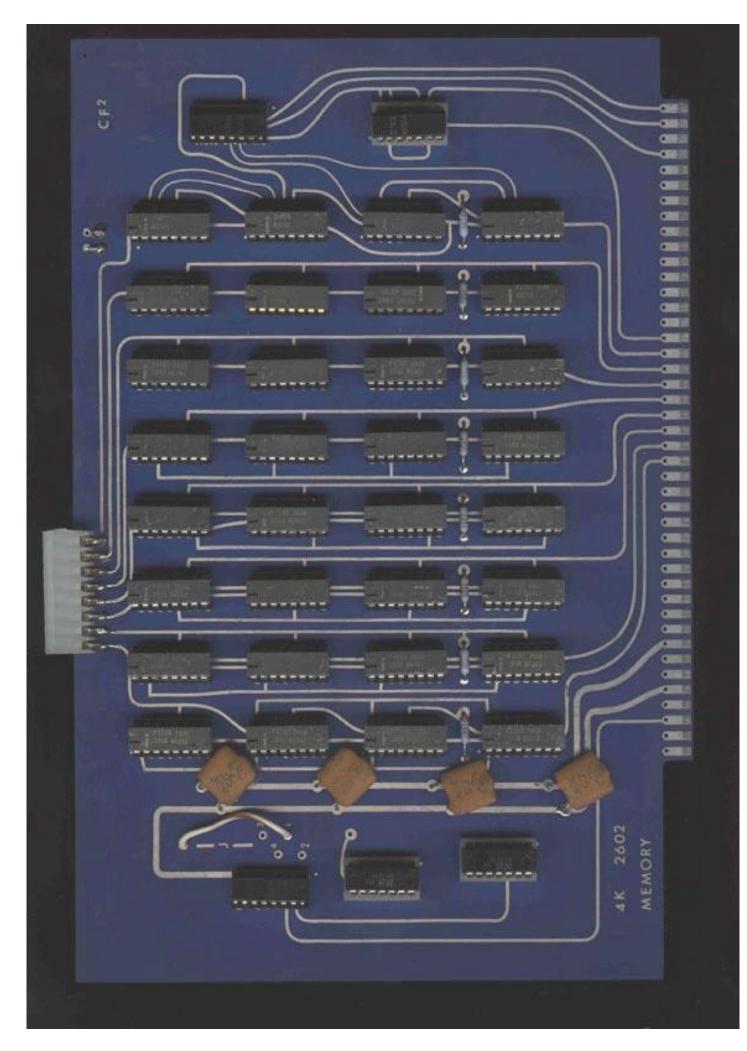

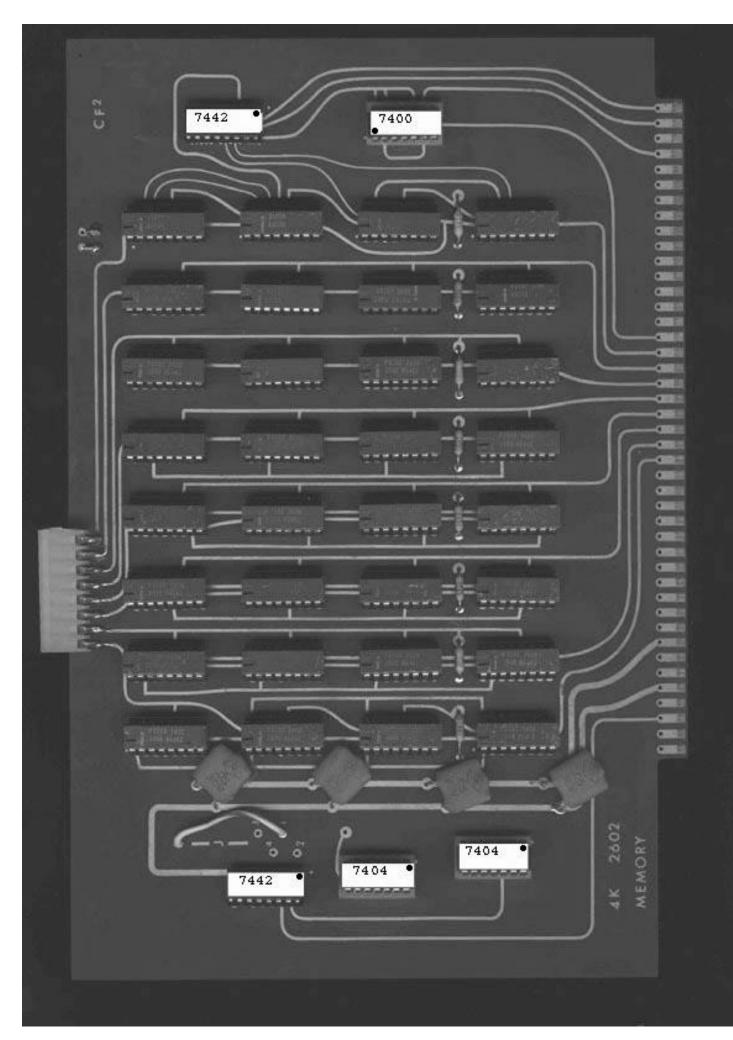

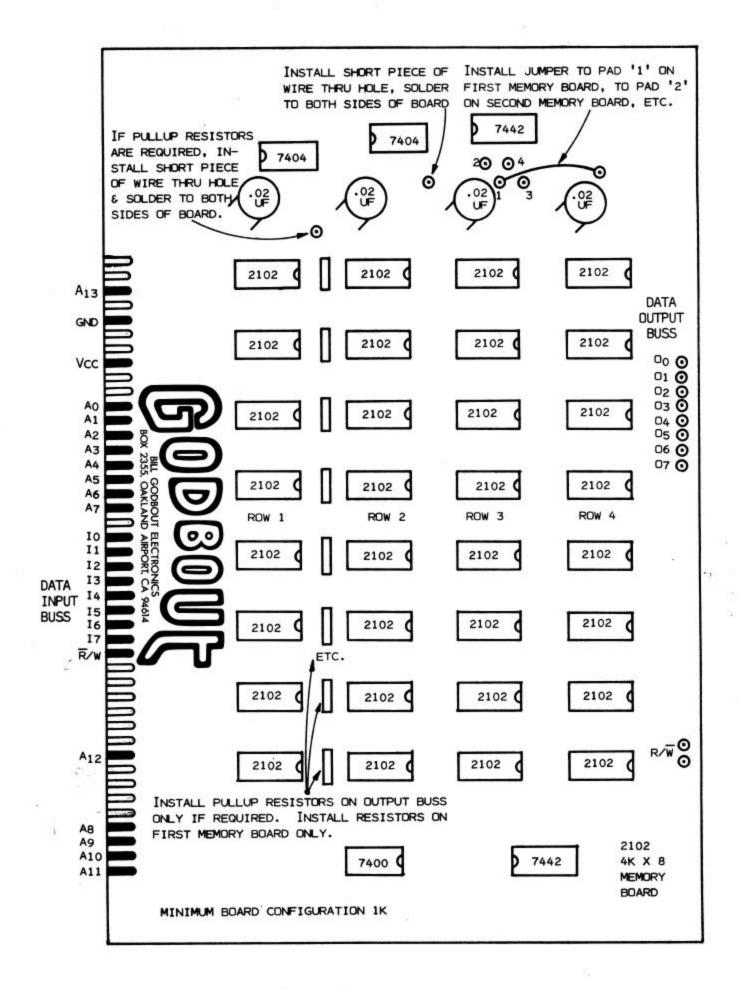

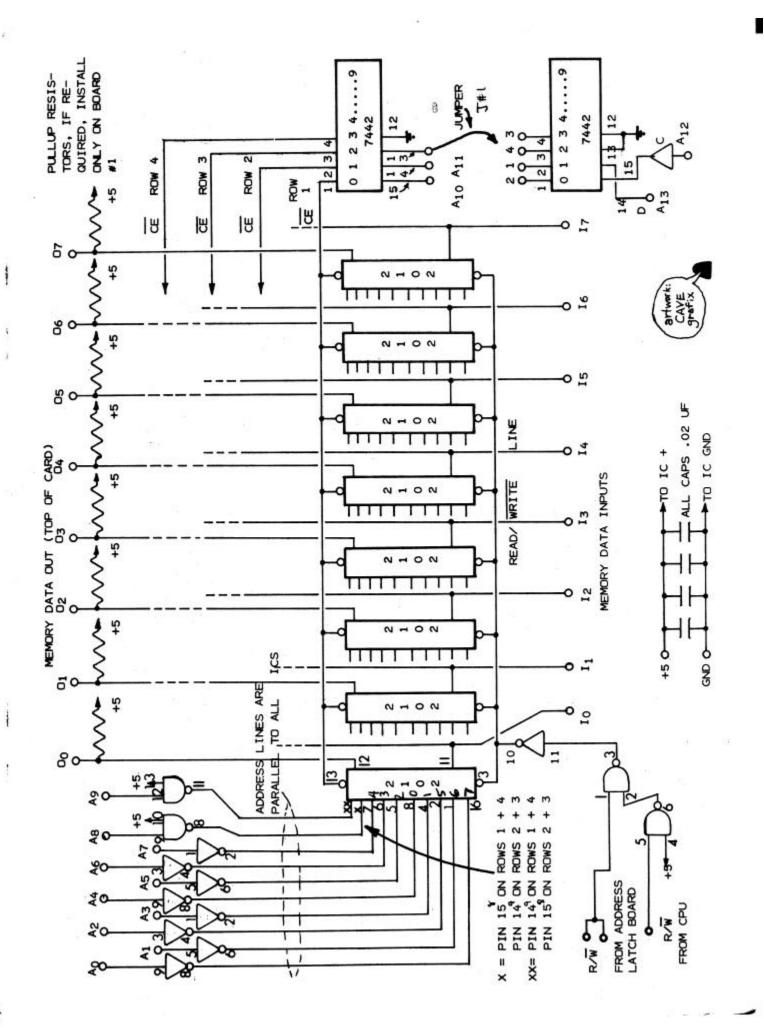

When I received my Mark-8 in little pieces from an eBay auction, I did not receive the original memory card. I received this one. It appears to have been made by Godbout Electronics, but confirmation is yet to come. It is certainly the same design, but is lacking the Godbout logo. Did Godbout buy this design from someone else? Did someone copy their design? If you would like to build one, there is enough information here to do so. I have included a few chip data sheets, they cmos versions, but the pinouts are the same. Good luck!

-Bryan

MERCHAN 4999 20 0 0 0 # 9 # 9 1444444 · 中国 电声量 第四 6 -0 0-0 0-0 e it presente a a 410 e=0

## MM54C42/MM74C42 BCD-to-Decimal Decoder

### **General Description**

The MM54C42/MM74C42 one-of-ten decoder is a monolithic complementary MOS (CMOS) integrated circuit constructed with N- and P-channel enhancement transistors. This decoder produces a logical "0" at the output corresponding to a four bit binary input from zero to nine, and a logical "1" at the other outputs. For binary inputs from ten to fifteen all outputs are logical "1".

High noise immunity

0.45 V<sub>CC</sub> (typ.)

■ Low power

50 nW (typ.)

■ Medium speed operation

10 MHz (typ.) with 10 V V<sub>CC</sub>

### **Features**

- Supply voltage range

- Tenth power TTL compatible

3V to 15V

drive 2 LPTTL loads

- Automotive

- Data terminals

**Applications**

- Instrumentation

- Medical electronics

- Alarm systems

- Industrial electronics

- Remote metering

- Computers

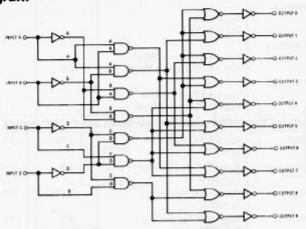

### Schematic Diagram

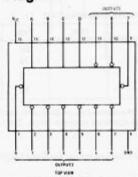

### Connection Diagram

### **Truth Table**

| INPUTS |     |   |    | OUTPUTS |   |   |    |   |   |   |   |    |   |

|--------|-----|---|----|---------|---|---|----|---|---|---|---|----|---|

| 0      | C   | 8 | Α, | 0       | 1 | 2 | 3  | 4 | 5 | 6 | 7 | 8  | 4 |

| 0      | 0   | 0 | D  | 0       | * | 1 | Ť. | 1 | 1 | 1 | 1 | 1  | 1 |

| 0      | 0   | 0 | 1  | 1       | 9 | 1 | 1  | 1 | × | 1 | 1 | 1  | 1 |

| 0      | 0   | ŧ | 0  | 1       | 1 | 0 | 1  | 1 | 1 | 1 | 4 | 1  |   |

| 0      | 0   | Ť | 1  | - 1     | 1 | 1 | 0  | 1 | A | 1 | 1 | 1  | 1 |

| 0      | 1   | 0 | 0  | 1       | 1 | 1 | 1  | Ü | 1 | 1 | 1 | 1  | 1 |

| 0      | 3   | 0 | 1  | 1       | 1 | 1 | 1  | 1 | 0 | 1 | 1 | 1  | 4 |

| 0      | 4   | 1 | 0  | 1       | 1 | 1 | 1  | 1 | 1 | O | 1 | 1  | × |

| 0      | - 1 | 1 | 1  | 1       | + | 1 | 1  | 1 | + | 1 | 0 | À. | 1 |

| 1      | 0   | Ü | 0  | 1       | 1 | 1 | 1  | 1 | 1 | 1 | 8 | 0  | I |

| 1      | 0   | 0 | 1  | 1       | 1 | 1 | 1  | 1 | 1 | 1 | 1 | 1  | 4 |

| 1      | 0   | 1 | 0  | 1       | 1 | 1 | 1  | 1 | 1 | 1 | 1 | 1  | 4 |

| 1      | 0   | 1 | 1  | 1.      | 1 |   | 1  | 1 | 1 | 1 | * | 1  | 1 |

| 1      |     | D | 0  | 1       | 1 | 1 | 1  | 1 | 1 | 1 | 1 | 1  | 1 |

| t      |     | 0 | 1  | 1       | 1 | 1 | 1  | 1 | 1 | 1 | 1 | +  | 1 |

|        |     | 1 | 0  | 3.      | 1 | 1 | 1  | 1 | 1 | + | 1 | +  | 1 |

| 1      |     | 4 | 1  | 1       | 1 | 1 | 1  | T | 1 | 1 | 1 | 1  | T |

# MM54C02/MM74C02 MM54C10/MM74C10

MM54C00/MM74C00 Quad 2-Input NAND Gate MM54C02/MM74C02 Quad 2-Input NOR Gate MM54C04/MM74C04 Hex Inverter MM54C10/MM74C10 Triple 3-Input NAND Gate MM54C20/MM74C20 Dual 4-Input NAND Gate

### **General Description**

These logic gates employ complementary MOS (CMOS) to achieve wide power supply operating range, low power consumption, high noise immunity and symmetric controlled rise and fall times. With features such as this the 54C/74C logic family is close to ideal for use in digital systems. Function and pin out compatibility with series 54/74 devices minimizes design time for those designers already familiar with the standard 54/74 logic family.

All inputs are protected from damage due to static discharge by diode clamps to V<sub>CC</sub> and GND.

### **Features**

3.0V to 15V Wide supply voltage range

1.0 V Guaranteed noise margin

High noise immunity 0.45 V<sub>CC</sub> (typ.)

Low power consumption 10 nW/package (typ.)

Low power fan out of 2 TTL compatibility driving 74L

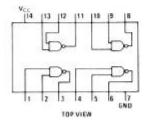

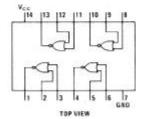

### Connection Diagrams

### MM54C00/MM74C00

### MM54C02/MM74C02

### MM54C04/MM74C04

### MM54C10/MM74C10

### MM54C20/MM74C20

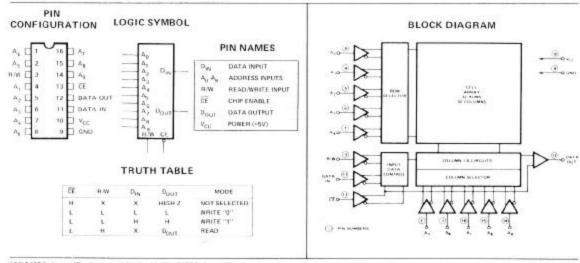

# 2102A, 2102AL/8102A-4\* 1K x 1 BIT STATIC RAM

| P/N      | Standby Pwr.<br>(mW) | Operating Pwr.<br>(mW) | Access<br>(ns) |  |

|----------|----------------------|------------------------|----------------|--|

| 2102AL-4 | 35                   | 174                    | 450            |  |

| 2102AL   | 35                   | 174                    | 350            |  |

| 2102AL-2 | 42                   | 342                    | 250            |  |

| 2102A-2  |                      | 342                    | 250            |  |

| 2102A    |                      | 289                    | 350            |  |

| 2102A-4  |                      | 289                    | 450            |  |

- Single +5 Volts Supply Voltage

- Directly TTL Compatible: All Inputs and Output

- Standby Power Mode (2102AL)

- Three-State Output: OR-Tie Capability

- Inputs Protected: All Inputs Have Protection Against Static Charge

- Low Cost Packaging: 16 Pin Dual-In-Line Configuration

The Intel® 2102A is a high speed 1024 word by one bit static random access memory element using N-channel MOS devices integrated on a monolithic array. It uses fully DC stable (static) circuitry and therefore requires no clocks or refreshing to operate. The data is read out nondestructively and has the same polarity as the input data.

The 2102A is designed for memory applications where high performance, low cost, large bit storage, and simple interfacing are important design objectives. A low standby power version (2102AL) is also available. It has all the same operating characteristics of the 2102A with the added feature of 35mW maximum power dissipation in standby and 174mW in operations.

It is directly TTL compatible in all respects; inputs, output, and a single +5 volt supply. A separate chip enable (CE) lead allows easy selection of an individual package when outputs are OR-tied.

The Intel® 2102A is fabricated with N-channel silicon gate technology. This technology allows the design and production of high performance easy to use MOS circuits and provides a higher functional density on a monolithic chip than either conventional MOS technology or P-channel silicon gate technology.

\*All 8102A-4 specifications are identical to the 2102A-4 specifications.